國立臺灣大學 109 學年度碩士班招生考試試題

423 科目: **應用電子學**

題號:423

節次:

題號:

共2页之第1页

## ※ 注意:請標明題號依序作答。

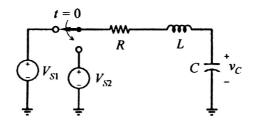

1. (25%) For t < 0, the circuit shown in Figure 1 is at DC steady state. Assume  $V_{S1} = 27$  V,  $V_{S2} = 12$  V, R = 12 200  $\Omega$ , L = 20 mH, and  $C = 0.1 \mu$ F. If the switch is thrown at t = 0,

- (a) (6%) Determine if the circuit is underdamped or overdamped for t > 0.

- (b) (5%) Find the capacitor voltage  $v_C$  at t = 0 and at  $t \to \infty$ , respectively.

- (c) (8%) Find the capacitor voltage  $v_C(t)$  at t > 0.

- (d) (6%) What is the minimum capacitor voltage  $v_{C,min}$  at t > 0?

Figure 1

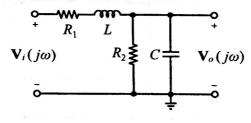

2. (15%) For the filter circuit shown in Figure 2:

Assume  $R_1 = 4.7 \text{ k}\Omega$ ,  $R_2 = 7.5 \text{ k}\Omega$ , L = 4 mH, and C = 0.33 nF.

- (a) (5%) Determine if this circuit is a low-pass, high-pass, bandpass, or handstop filter.

- (b) (10%) Compute the frequency response function and determine  $|V_0/V_1|$  at  $\omega = 10^6$  rad/s.

Figure 2

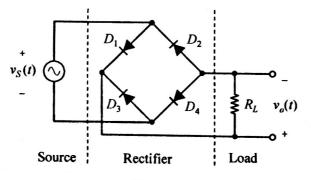

- 3. (20%) A wave rectifier is shown in the circuit of Figure 3. Assume that a step-down transformer supplies 15 V rms to the rectifier.

- (a) (6%) If the diodes have an offset voltage of 0.7 V, sketch the input source voltage  $v_S(t)$  and the output voltage  $v_0(t)$ , and state which diodes are on and which are off in the appropriate cycles of  $v_S(t)$ . The frequency of the source is 60 Hz.

- (b) (7%) If  $R_L = 2.2 \text{ k}\Omega$  and a filtering capacitor has a value of 2.5  $\mu$ F, sketch the output voltage  $v_o(t)$ .

- (c) (7%) Repeat (b), with the capacitance equal to  $100 \mu F$ .

Figure 3

節次: 7

共2頁之第2頁

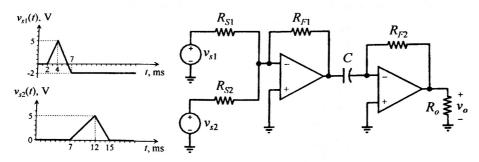

4. (20%) For the given source voltages  $v_{s1}$  and  $v_{s2}$  of the circuit shown in Figure 4, please determine the output voltage  $v_o$  as a function of time and plot it. Assume ideal operational amplifiers are used.  $R_{S1} = R_{S2} = R_{F1} = R_{F2} = R_o = 4 \text{ k}\Omega$  and  $C = 250 \mu\text{F}$ .

Figure 4

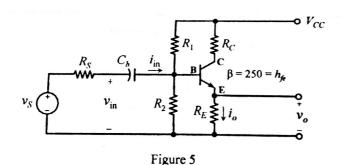

- 5. (20%) The circuit shown in Figure 5 is similar to a common collector implemented with an *npn* silicon transistor and a single DC supply  $V_{CC} = 15$  V.  $v_S$  is a small sine wave signal with average value of  $V_{DC}$ . If  $R_1 = 12$  k $\Omega$ ,  $R_2 = 8$  k $\Omega$ ,  $R_C = 50$   $\Omega$ ,  $R_E = 250$   $\Omega$  and  $C_b = \infty$ ,

- (a) (7%) Determine the voltage across the collector and emitter,  $V_{CE}$  at the operating point Q of the transistor.

- **(b)**(7%) Find the voltage gain  $v_o/v_{in}$ .

- (c) (6%) Find the current gain  $i_o/i_{in}$

試題隨卷繳回